### MCD2006G/T/R

## PLL ICs with Integrated VCO for FM/FSK Transceiver

### **General Description**

MCD2006G/T/R is a set of ICs for FM/FSK wireless transceiver intended for use in the VHF band, MCD2006G and MCD2006T are applied in transmitter, and MCD2006R is used in receiver. Three ICs contain an integrated VCO, a RF power amplifier, a reference crystal oscillator, and a frequency synthesizer. A completed phase-lock-loop (PLL) is consisted by combining the ICs and on board LPF, inductor and varactors.

The difference MCD2006G between and MCD2006T/R is T/R contains a 6-bit ROM, the PLL can be locked at corresponding frequencies when users setup 6-bit ROM logic input shown in fixed logic table in appendix. The frequencies MCD2006T between and MCD2006R corresponding each other with a 455KHz frequency difference. MCD2006G contains **MCU** programmable control interface which is used for setting division for any targeted frequency between 3MHz~110MHz by an external MCU.

In practical terms MCD2006G must combine with a MCU but MCD2006T/R can be free of MCU.

Supply voltage range is 2.7 to 4.5 volts. It has been proved that MCD2006G/T/R can work stably between -40 to +85 degrees.

### **Typical Applications**

- FM transceiver, remote controller

- 27-49M baby monitor, PTT and car radio

- Infrared FM transceiver system

#### **Features**

■ Operating Frequency:

MCD2006G: 3MHz~110MHz

MCD2006T/R: fixed frequencies shown in the

logic table in appendix

20MHz crystal is a must for 3.2~8.0MHz

4MHz crystal is a must for 40.660~54.405MHz

■ Operating Voltage Range: 2.7~4.5V (3.3V Typical)

Operating Power Consumption: MCD2006G/T: 19mA@3.3V, 27MHz

MCD2006R: 12mA@3.3V, 27MHz

■ The crystal oscillator supports:

MCD2006G: 4~25MHz

MCD2006T/R:

4MHz (for 5KHz reference frequency) 20MHz (for 25KHz reference frequency)

■ RF output power(50Ω output impedance) MCD2006G/T: 3dBm@27MHz

$MCD2006R:\ -15dBm@27MHz$

■ Low phase noise: -112dBc/Hz at 10KHz offset, 50Hz loop bandwidth

■ TX Modulation: FM/FSK

■ RF AMP Output Distortion: <1%

■ Modulated Deviation: 5KHz reachable

Modulated Audio Frequency Range: 50Hz~30KHz

■ Data Rate: 300bps~120kbps

■ Package:

MCD2006G: TSSOP-16 MCD2006T/R: QFN-20L

**Version History**

| Version | Issued time   | Notes                                      |

|---------|---------------|--------------------------------------------|

| V1.0    | Oct. 28, 2006 | First English version created              |

| V1.1    | Aug. 29, 2008 | Add MCD2006S                               |

| V1.2    | May 01, 2010  | Change MCD2006S package to QFN20L          |

| V1.3    | Nov. 20, 2012 | Update MCD2006S to MCD2006T, add MCD2006R. |

1

www.mcdevices.com

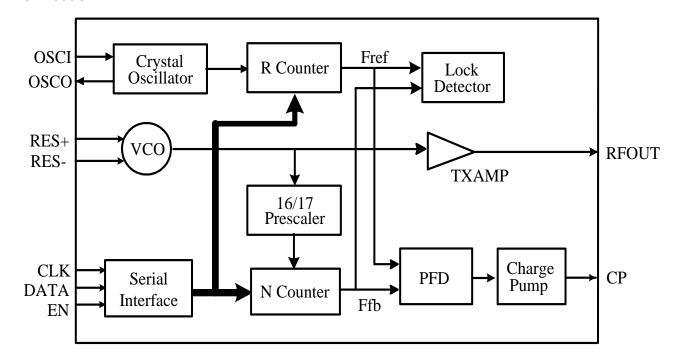

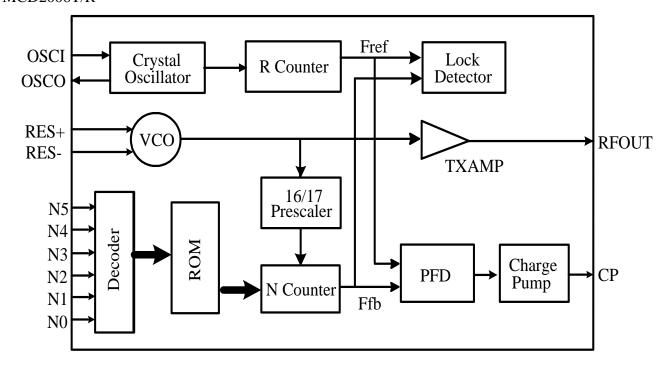

### **Function Block Diagram**

■ MCD2006G

### ■ MCD2006T/R

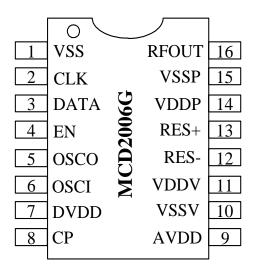

### **Pin Assignment and Description**

■ MCD2006G

| Pin# | Pin Name | I/O | Description                                                                                                                                                                              |

|------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | VSS      | I   | Terminal of PLL ground.                                                                                                                                                                  |

| 2    | CLK      | I   | MCU control clock input. Data are clocked in on the rising edges of the clock.                                                                                                           |

| 3    | DATA     | I   | MCU serial data input. LSB are sent in first and last two bits are group code.                                                                                                           |

| 4    | EN       | I   | MCU control enable input. When EN is high level, the data saved in shift register is loaded into appropriate counter (determined by group code).                                         |

| 5    | OSCO     | О   | Output terminal of crystal oscillator. This pin is connected to the crystal when the reference frequency is generated by the crystal oscillator.                                         |

| 6    | OSCI     | I   | Input terminal of crystal oscillator. The pin is connected to the crystal when the reference frequency is generated by the local oscillator. It also can be driven by an external clock. |

| 7    | DVDD     | I   | Digital circuit power supply (2.7-4.5V).                                                                                                                                                 |

| 8    | СР       | О   | Output terminal of charge pump. Connecting to the loop filter to drive the voltage control input of the VCO.                                                                             |

| 9    | AVDD     | I   | Analogue circuit power supply (2.7-4.5V).                                                                                                                                                |

| 10   | VSSV     | I   | Terminal of VCO ground.                                                                                                                                                                  |

| 11   | VDDV     | I   | VCO circuit power supply (2.7-4.5V).                                                                                                                                                     |

| 12   | RES-     | I   | The RES pins are used to supply DC voltage to the VCO, as well as to tune the centre frequency of the VCO. Equal value capacitors should be connected to this pin and pin 13.            |

| 13   | RES+     | I   | Same as pin12.                                                                                                                                                                           |

| 14   | VDDP     | I   | RF power amplifier circuit power supply (2.7-4.5V).                                                                                                                                      |

| 15   | VSSP     | I   | Terminal of RF power amplifier ground.                                                                                                                                                   |

| 16   | RFOUT    | О   | RF output pin. Typical output power is $3dBm@27MHz$ with $50\Omega$ output impedance.                                                                                                    |

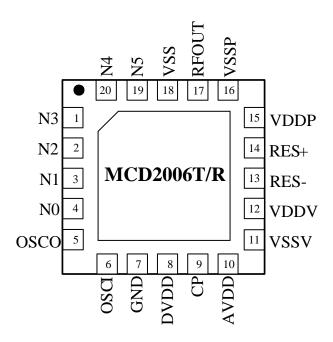

■ MCD2006T/R

| Pin#  | Pin Name | I/O | Description                                                                                         |  |                                                                            |

|-------|----------|-----|-----------------------------------------------------------------------------------------------------|--|----------------------------------------------------------------------------|

| 19~20 | N5~N0    | I   | 6 <sup>th</sup> ~1 <sup>st</sup> ROM control bit. When the pin floats, the logic level is low, when |  |                                                                            |

| 1~4   | 113~110  | 1   | the pin is connected to VDD, the logic level is high.                                               |  |                                                                            |

| 5     | OSCO     | 0   | Output terminal of crystal oscillator. This pin is connected to the crystal                         |  |                                                                            |

| 3     | OSCO     | 0   | when the reference frequency is generated by the crystal oscillator.                                |  |                                                                            |

|       |          |     | Input terminal of crystal oscillator. The pin is connected to the crystal                           |  |                                                                            |

| 6     | OSCI     | I   | when the reference frequency is generated by the local oscillator. It also                          |  |                                                                            |

|       |          |     | can be driven by an external clock.                                                                 |  |                                                                            |

| 7     | GND      | I   | Terminal of ground.                                                                                 |  |                                                                            |

| 8     | DVDD     | I   | Digital circuit power supply (2.7-4.5V).                                                            |  |                                                                            |

| 0     | 9 CP O   |     | Output terminal of charge pump. Connecting to the loop filter to                                    |  | Output terminal of charge pump. Connecting to the loop filter to drive the |

| 9     |          |     | voltage control input of the VCO.                                                                   |  |                                                                            |

| 10    | AVDD     | I   | Analogue circuit power supply (2.7-4.5V).                                                           |  |                                                                            |

| 11    | VSSV     | I   | Terminal of VCO ground.                                                                             |  |                                                                            |

| 12    | VDDV     | I   | VCO circuit power supply (2.7-4.5V).                                                                |  |                                                                            |

|       |          |     | The RES pins are used to supply DC voltage to the VCO, as well as to                                |  |                                                                            |

| 13    | RES-     | I   | tune the centre frequency of the VCO. Equal value capacitors should be                              |  |                                                                            |

|       |          |     | connected to this pin and pin 16.                                                                   |  |                                                                            |

| 14    | RES+     | I   | Same as pin15.                                                                                      |  |                                                                            |

| 15    | VDDP     | I   | RF power amplifier circuit power supply (2.7-4.5V).                                                 |  |                                                                            |

| 16    | VSSP     | I   | Terminal of RF power amplifier ground.                                                              |  |                                                                            |

| 17    | RFOUT    | 0   | RF output pin. Typical output power is 4dBm@49MHz with 50Ω output                                   |  |                                                                            |

| 1 /   | Kroui    |     | impedance.                                                                                          |  |                                                                            |

| 18    | VSS      | I   | Terminal of analogue circuit ground.                                                                |  |                                                                            |

### **Recommended Operating Conditions**

| Domonoton             | Cymbal  |     | I Init  |     |            |

|-----------------------|---------|-----|---------|-----|------------|

| Parameter             | Symbol  | Min | Typical | Max | Unit       |

| Power Supply Voltage  | VDD     | 2.7 | 3.3     | 4.5 | V          |

| Operating Temperature | $T_{A}$ | -40 | 27      | +85 | $^{\circ}$ |

### **Electrical Characteristics** (VDD=3.3V, -40 $^{\circ}$ C $\leq$ T<sub>A</sub> $\leq$ +85 $^{\circ}$ C; except as specified)

| Symbol            | Parameter                                  | Cone                    | ditions                   | Min    | Тур     | Max     | Units |  |

|-------------------|--------------------------------------------|-------------------------|---------------------------|--------|---------|---------|-------|--|

| Genera            | l Characteristics                          |                         |                           |        |         |         |       |  |

|                   |                                            | MCD                     | 3                         | 27     | 110     |         |       |  |

| $F_{OUT}$         | Operating Frequency                        | MCD2006T/R              | 20MHz crystal             | 3.2    |         | 8.0     | MHz   |  |

| 1.OUT             | Operating Frequency                        | (see the appendix)      | 4MHz crystal              | 40.660 |         | 54.405  | WITIZ |  |

|                   |                                            | MCD                     | 2006G                     | 4      |         | 25      |       |  |

| F <sub>OSC</sub>  | Crystal Frequency                          | MCD200CT/D              | 5KHz reference frequency  | /      | 4       | /       | MHz   |  |

|                   |                                            | MCD2006T/R              | 25KHz reference frequency | /      | 20      | /       |       |  |

|                   | DI D                                       | MCD                     | 2006G                     | se     | t by us | ers     |       |  |

| $F_{PD}$          | Phase Detector                             | MCD2006F/D              | 4MHz crystal              | /      | 5       | /       | KHz   |  |

|                   | Frequency                                  | MCD2006T/R              | 20MHz crystal             | /      | 25      | /       |       |  |

| $V_{IH}$          | High-Level Input Voltage                   |                         |                           | 0.8    |         | 1       | VDD   |  |

| $V_{\mathrm{IL}}$ | Low-Level Input Voltage                    |                         |                           | 0.1    |         | 0.3     | V     |  |

|                   | Power Consumption                          |                         | F <sub>OUT</sub> =27MHz   |        | 19      |         |       |  |

| т                 |                                            | MCD2006G/T              | F <sub>OUT</sub> =49MHz   |        | 17      |         | mA    |  |

| $I_{DD}$          |                                            |                         | $F_{OUT} = 100MHz$        |        | 18      |         | ша    |  |

|                   |                                            | MCD2006R                | $F_{OUT} = 27MHz$         |        | 12      |         |       |  |

| $I_{CP}$          | Charge Pump Current                        |                         |                           |        | ±800    |         | uA    |  |

| RF Cha            | aracteristics                              |                         |                           |        |         |         |       |  |

| $V_{CP}$          | VCO Control Voltage                        |                         |                           | 0.5    |         | VDD-1.0 | V     |  |

| 1                 |                                            | F <sub>OUT</sub> =      | =27MHz                    |        | 3       |         |       |  |

| $P_{OUT}$         | Output Power                               | F <sub>OUT</sub> =      | =49MHz                    |        | 4       |         | dBm   |  |

|                   |                                            | $F_{OUT} =$             |                           | 5      |         |         |       |  |

|                   |                                            | E 27MH-                 | 2nd Harmonic<br>50Ω Load  |        | -54     |         |       |  |

|                   | Harmonic Suppression (The matching network | F <sub>OUT</sub> =27MHz | 3rd Harmonic 50Ω Load     |        | -53     |         |       |  |

| HS <sub>OUT</sub> | is shown in                                | E 40MI                  | 2nd Harmonic<br>50Ω Load  |        | -57     |         | dBm   |  |

|                   |                                            | F <sub>OUT</sub> =49MHz | 3rd Harmonic<br>50Ω Load  |        | -59     |         |       |  |

| Symbol                     |                                            |                         |                         |       |            |       |        |  |  |  |  |  |

|----------------------------|--------------------------------------------|-------------------------|-------------------------|-------|------------|-------|--------|--|--|--|--|--|

| -                          | Parameter                                  | Condi                   | tions                   | Min   | Тур        | Max   | Units  |  |  |  |  |  |

|                            |                                            |                         | 2nd Harmonic            |       | -53        |       |        |  |  |  |  |  |

|                            |                                            | F <sub>OUT</sub>        | 50Ω Load                |       | -33        |       |        |  |  |  |  |  |

|                            |                                            | =100MHz                 | 3rd Harmonic            |       | <i>5</i> 1 |       | 1D     |  |  |  |  |  |

|                            |                                            |                         | $50\Omega$ Load         |       | -54        |       | dBm    |  |  |  |  |  |

| IZ.                        | Fine Tuning Sensitivity                    | F <sub>OUT</sub> =2     | 7MHz                    |       | 3          |       | MHz/V  |  |  |  |  |  |

| K <sub>VCO</sub>           | (varactor ISV149)                          | F <sub>OUT</sub> =4     | 9MHz                    |       | 900        |       | KHz/V  |  |  |  |  |  |

| Z <sub>OUT</sub>           | Output Impedance                           |                         |                         |       | 50         |       | Ω      |  |  |  |  |  |

|                            |                                            |                         | 1KHz offset             |       | -88        |       |        |  |  |  |  |  |

|                            |                                            | $F_{OUT} = 27MHz$       | 10KHz offset            |       | -112       |       |        |  |  |  |  |  |

|                            | Phase Noise                                |                         | 100KHz offset           |       | -124       |       |        |  |  |  |  |  |

|                            |                                            |                         | 1KHz offset             |       | -77        |       | dBc/Hz |  |  |  |  |  |

| PN <sub>OUT</sub>          |                                            | F <sub>OUT</sub> =49MHz | 10KHz offset            |       | -106       |       |        |  |  |  |  |  |

|                            |                                            |                         | 100KHz offset           |       | -116       |       |        |  |  |  |  |  |

|                            |                                            |                         | 1KHz offset             |       | -77        |       |        |  |  |  |  |  |

|                            |                                            | $F_{OUT} = 100MHz$      | 10KHz offset            |       | -104       |       |        |  |  |  |  |  |

|                            |                                            |                         | 100KHz offset           |       | -124       |       |        |  |  |  |  |  |

| Modulat                    | tion (TX)                                  |                         |                         | •     |            |       | •      |  |  |  |  |  |

| $S_{AF}$                   | Audio Frequency Range                      |                         |                         | 50    |            | 30K   | Hz     |  |  |  |  |  |

| $S_{DR}$                   | Data Rate                                  |                         |                         | 300   |            | 120K  | bps    |  |  |  |  |  |

| Б                          | FM Deviation                               | $F_{OUT} = 2$           | 27MHz                   | 0.035 |            | 0.045 | 1711   |  |  |  |  |  |

| $\mathrm{D}_{\mathrm{EV}}$ | (1SV149, 300~3K BPF)                       | $F_{OUT} = 4$           | l9MHz                   | 0.03  |            | 0.04  | KHz    |  |  |  |  |  |

| Б                          | M 11 ( 1D ' ' '                            | 26mV amplitude,         | $F_{OUT} = 27MHz$       |       | ±3         |       | 1711   |  |  |  |  |  |

| $F_{MD}$                   | Modulated Deviation                        | 23mV amplitude,         | F <sub>OUT</sub> =49MHz |       | ±3         |       | KHz    |  |  |  |  |  |

|                            | S/N                                        | $F_{OUT} = 27MHz$       |                         |       | 44         |       |        |  |  |  |  |  |

| SNR                        | (3KHz modulation-port character,300~3KBPF) | F <sub>OUT</sub> =4     |                         | 44    |            | dB    |        |  |  |  |  |  |

| DIST                       | Audio Distortion                           | demodul                 | ated AF                 |       |            | 1.0   | %      |  |  |  |  |  |

### 1. Function Description

#### 1.1 ROM mode

MCD2006T/R works at ROM mode only. The 6-bit input data N0-N5 is decoded to 64 control lines by X-Y crossed combination. The 64 lines correspond to 64 18-bit parallel outputs which are sent to prescaler and counters.

64 channels are partitioned to 4 groups, which are shown in appendix in detailed. Users set the logic level of N0~N5 according to the logic table, PLL will lock at the corresponding frequency.

The frequencies in Group A and B in MCD2006T are set for IR FM transmitter whose reference frequency is chosen as 25KHz. While frequencies in Group C and D are set for baby monitor system whose reference frequency is chosen as 5KHz.

The frequencies in Group A,B,C and D in MCD2006R are all set for baby monitor system with a fixed 5KHz reference frequency. The frequencies in Group A are corresponding to the frequencies in MCD2006T Group C with a 4.455MHz frequency difference. Same situation between Group B and MCD2006T Group D. The frequencies in Group C and D are corresponding to the frequencies in MCD2006T Group C and D with a 455KHz frequency difference.

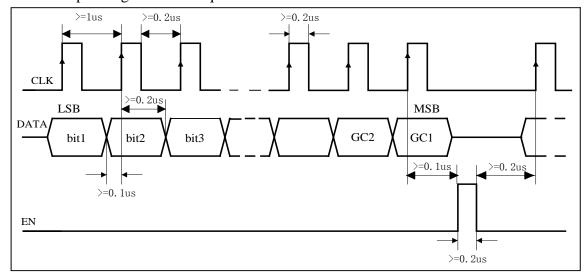

1.2 MCU mode

MCD2006G works at MCU mode only. The CLK, DATA, and EN pins are used for serial data interface Rinary serial data enter via the DATA pin,

interface. Binary serial data enter via the DATA pin, go through serial-to-parallel interface to configure reference counter and channel N counter separately according to the group code.

Data shift in shift register at the rising edge of the CLK signal. Firstly LSB data are shifted in, and then the last two bits (group code) decode the internal register address. At the rising edge of EN signal, shifted data are loaded into one of the two appropriate counters.

The input CLK, DATA and EN timing should follow drawing diagram.

**Notes:**

- (1) LSB data are shifted in first.

- (2) When power up, usually R counter is configured before N counter.

### Group code assignment:

| GROUI     | CODE      | LOCATION                         |  |  |  |  |

|-----------|-----------|----------------------------------|--|--|--|--|

| GC1 (MSB) | GC2 (LSB) | LOCATION                         |  |  |  |  |

| 0         | 0         | Control Latch(test purpose only) |  |  |  |  |

| 1         | 0         | Channel N counter                |  |  |  |  |

| 1         | 1         | Reference counter                |  |  |  |  |

7

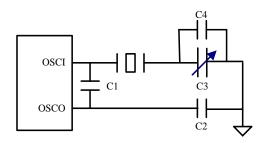

#### 1.3 Reference Oscillator

The reference frequency for PLL is obtained by applying an external crystal and a few capacitors. External capacitors C1 to C4 are required to set the proper crystal's load capacitance and oscillation frequency. MCD2006S has to apply 4MHz crystal for getting a 5KHz reference frequency or 20MHz crystal for getting a 25KHz reference frequency.

#### 1.4 Reference Divider (R counter)

The reference divider provides reference frequency for PFD (Phase Frequency Detector). It includes a fixed 1/2 divider and a 10-bit programmable divider. The 10-bit divider can program the division ratio between 3 and 1023. Due to the fixed 1/2 divider, the total division ratio for reference divider will range from 6 to 2046.

The division ratio of MCD2006T/R is fixed at 800 internally, so a 4MHz crystal is a must to create 5KHz reference frequency, and a 20MHz crystal is a must to create 25KHz reference frequency.

The division ratio of MCD2006G is set by an external MCU. See the programming description at Section 2 for details.

#### 1.5 Feedback Divider (N counter)

The channel N counter is clocked by the RF signal generated by VCO. The N counter consists of a 4-bit swallow counter with a division ratio 0<A<15 and a 12-bit pulse counter with a division ratio 3<B<4095. In conjunction with the 16/17 prescaler, the total division ratio can range from 48 to 65535 on the feedback channel. For the proper operation of the prescaler, the pulse counter division ratio B should be always equal to or greater than the swallow counter division ratio A.

The division ratio of MCD2006T/R is set by ROM.

Users simply set the input level of N0-N5 following the logic table, the internal decoder and ROM will read appropriate division ratio and send it to the N counter. There is no calculation and configuration requirement for the users. When choosing frequency in the range of 3.2~8.0MHz, a 20MHz crystal is a must. While a 4MHz crystal is a must when selecting frequency in the range of 40.660~54.405MHz.

The division ratio of MCD2006G is determined by an external MCU. See the programming description at Section 2 for details.

#### 1.6 Prescaler

The prescaler of MCD2006G/T/R consists of a pre-amplifier, and a CMOS 16/17 dual modulus divider. The prescaler offers clock to the subsequent CMOS N counter.

#### 1.7 Phase/Frequency Detector (PFD)

PFD compares frequency and phase of two inputs from reference counter and N counter, outputs control logic to charge pump. The PFD receives a feedback signal from charge pump in order to eliminate dead zone.

#### 1.8 Charge Pump

The charge pump pumps **u**p current to an external loop filter, or pumps down from the filter according to the polarity control of its PFD outputs. The loop filter converts the charge into VCO's control voltage. The charge pump steers the charge pump output CP to VDD (pump-up) or GND (pump-down). Under the locked condition, CP is primarily in a TRI-STATE mode with small corrections. The charge pump current magnitude is ±800uA.

#### 1.9 VCO

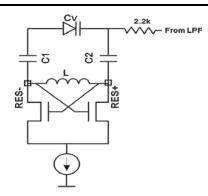

VCO is a tuned differential amplifier with the gate and drain cross coupled to provide positive feedback and a 360° phase shift (shown in the following picture). It is comprised an external inductor, two capacitors, two varactors and internal circuits. The users need to select appropriate inductors for the desired frequency of operation. The output of the VCO is applied to the TXAMP and buffered to prescaler circuit, where it is divided down and compared to the reference frequency.

The setup of the VCO can be summarized as follows. Firstly, open the loop, build up an oscillation (as shown in above picture). Two capacitors connected at pin RES- and RES+ are recommended as 100~120pF (when loop locked at 49MHz). The inductor connected between pin RES- and RES+ need to be calculated according to following equation.

$$L = \left(\frac{1}{2\pi f}\right)^2 \frac{1}{C}$$

$$C = C1 \text{ or } C2 //Cv$$

Cv: varactor capacitance corresponding to applied LPF voltage, check varactor datasheet.

In above equation, the value of C is the amount of capacitance presented by varactors, capacitors and parasitic. For rough calculation, the parasitic value

can be ignored.

Define the VCO frequency as the lowest frequency F1 when setting the negative end of Cv to 0V, define the VCO frequency as the highest frequency F2 when setting the negative end of Cv to VDD. F1 and F2 determine VCO frequency range. Users need to guarantee the targeted frequency is within the range, staying at middle is recommended.

Secondly, add LPF in to become a close loop (shown in application circuit). At this moment, the voltage level of the negative end of Cv is controlled by the added LPF, when this voltage fixes at a stable level, the loop locks. The voltage level of LPF should be within the control voltage range of VCO.

#### **1.10 TXAMP**

The RF amplifier is an output stage. The amplifier of MCD2006G/T is capable of providing 4dBm output power to a 50ohm load while operating at 3.3V power supply, the MCD2006R is able to provide -15dBm output power.

### 2. Programming Description

#### 2.1 Reference counter

The reference counter provides reference frequency for PLL. It includes a fixed 1/2 divider and a 10-bit programmable divider. The 10-bit divider can program the division ratio between 3 and 1023. Due to the fixed 1/2 divider, the total division ratio for reference divider can be set from 6 to 2046.

LSB

Configuration word

**MSB**

Division ratio of the programmable 10bit R counter:

| Division ratio (R) | R10 | R9 | R8 | R7 | R6 | R5 | R4 | R3 | R2 | R1 |

|--------------------|-----|----|----|----|----|----|----|----|----|----|

| 3                  | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  |

| 4                  | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | 0  |

| •                  | •   | •  | •  | •  | •  | •  | •  | •  | •  | •  |

| 1023               | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

$$R = R1x2^{0} + R2x2^{1} + ... + R10x2^{9} (R \ge 3)$$

The total division ratio range: 6 to 2046.

#### 2.2 Channel N counter

This programmable counter is composed of a 4-bit swallow counter and a 12-bit pulse counter, in conjunction with the 16/17 prescaler to provide division ratio range from 48 to 65535.

LSB configuration word MSB

| N1 N2 N3 N4 N5 N6 N7 N8 N9 N10 N11 N12 N13 N14 N15 N16 GC2=0 G |

|----------------------------------------------------------------|

|----------------------------------------------------------------|

|-----swallow counter-----|-----group code-----|

#### Swallow counter division ratio (A)

| Division ratio (A) | N4 | N3 | N2 | N1 |

|--------------------|----|----|----|----|

| 0                  | 0  | 0  | 0  | 0  |

| 1                  | 0  | 0  | 0  | 1  |

| •                  | •  | •  | •  | •  |

| 15                 | 1  | 1  | 1  | 1  |

$$A = N1x2^0 + N2x2^1 + ... + N4x2^3$$

Division ratio range: 0 to 15

#### Pulse counter division ratio (B)

| Division ratio (B) | N16 | N15 | N14 | N13 | N12 | N11 | N10 | N9 | N8 | N7 | N6 | N5 |

|--------------------|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|

| 3                  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 1  | 1  |

| 4                  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 1  | 0  | 0  |

| •                  | •   | •   | •   | •   | •   | •   | •   | •  | •  | •  | •  | •  |

| 4095               | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  |

$$B = N5x2^0 + N6x2^1 + ... + N16x2^{11}$$

Division ratio range: 3 to 4095 (B≥A)

Total division ratio of programmable N counter:

N = 16 \* B + A (B $\ge$ A)

Division ratio range: 48 to 65535

### 3. Configuration Examples

**Example A:** To get a 5KHz reference frequency from a 4MHz crystal

■ Total division ratio  $2R = 4MHz \div 5KHz = 800$

■ Programmable division ratio  $R = 800 \div 2 = 400$

■ Binary format (10bit) R=0110010000

■ Group code "11"

■ Configuration word(12bit) "110110010000"

LSB(first in)  $\rightarrow$  MSB

0 0 0 0 1 0 0 1 1 1

**Example B:** To synthesize a 40.665MHz frequency from a 5KHz reference frequency

- Reference frequency 5KHz (see Example A)

- Total division ratio  $16*B + A = 40.665MHz \div 5KHz = 8133$

- Pulse counter division ratio  $B = Int (8133 \div 16) = 508$

- Binary format (12-bit) B = 0001111111100

- Swallow counter division ratio A = 8133 16\*508 = 5

- Binary format (4bit) A=0101

- Group code "10"

- Configuration word(18bit) "1000011111111000101"

$LSB(first in) \rightarrow MSB$

1 0 1 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0 1

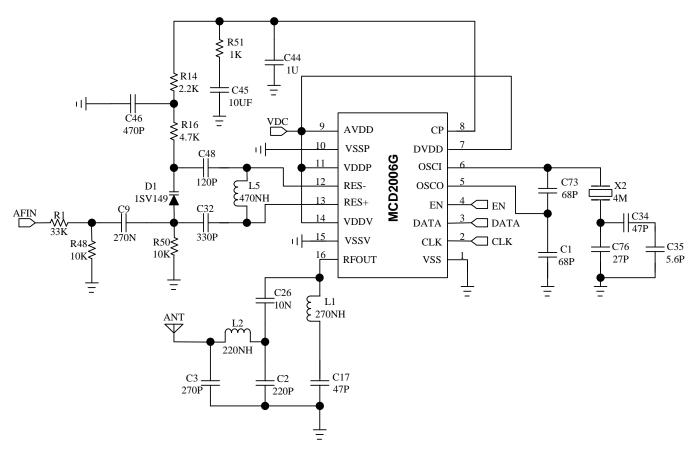

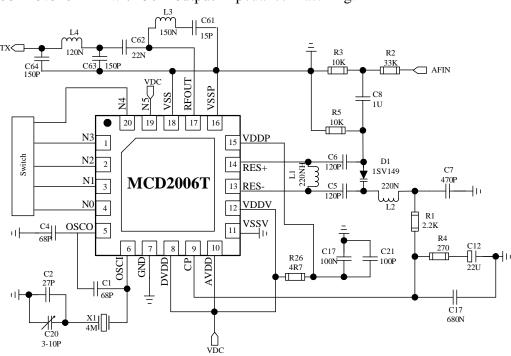

### 4. Typical Application Circuit

### Reference Schematic

■ For MCD2006G 27MHz with  $50\Omega$  output impedance matching:

■ For MCD2006T 49.840MHz with  $50\Omega$  output impedance matching:

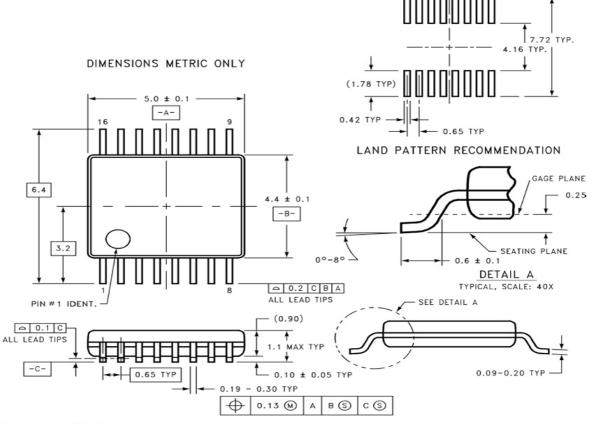

### **5. Package Dimensions**

■ TSSOP-16

Dimensions are in millimeters.

16-Pin TSSOP Package

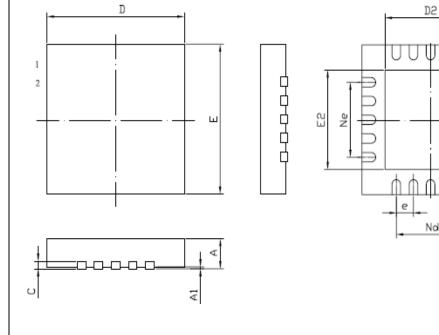

#### QFN-20L

| SYMBOL           | М              | ILLIMETE | ER   |  |  |  |  |

|------------------|----------------|----------|------|--|--|--|--|

| SIMBOL           | MIN            | NOM      | MAX  |  |  |  |  |

| A                | 0.70           | 0.75     | 0.80 |  |  |  |  |

| Al               | ı              | 0.01     | 0.05 |  |  |  |  |

| b                | 0.18           | 0.25     | 0.30 |  |  |  |  |

| c                | 0.18           | 0.20     | 0.25 |  |  |  |  |

| D                | 3.90           | 4.00     | 4.10 |  |  |  |  |

| D2               | 2. 65REF       |          |      |  |  |  |  |

| e                | 0              | . 50BSC  |      |  |  |  |  |

| Ne               | 2              | 2. 00BSC |      |  |  |  |  |

| Nd               | - 1            | 2. 00BSC |      |  |  |  |  |

| E                | 3. 90          | 4.00     | 4.10 |  |  |  |  |

| E2               | 2              | 2. 65REF |      |  |  |  |  |

| L                | 0.35           | 0.40     | 0.45 |  |  |  |  |

| h                | 0.30 0.35 0.40 |          |      |  |  |  |  |

| L/F载体尺寸<br>(mil) | 1              | 114x114  |      |  |  |  |  |

|                  |                |          |      |  |  |  |  |

### Appendix1: MCD2006T ROM logic table

**Note:**

- (1) The background letters A~D denote channel group

- (2) When choosing group A and B, a 20MHz crystal is a must. While a 4MHz crystal is a must when selecting group C and D.

- (3) When pin N0-N5 float, the logic level is low, when the pin is connected to VDD, the logic level is high.

| level is nigh. |    |    |    |    |    |    |        |    |    |    |    |    |    |    |        |

|----------------|----|----|----|----|----|----|--------|----|----|----|----|----|----|----|--------|

| No             | N5 | N4 | N3 | N2 | N1 | N0 | Fvco   | No | N5 | N4 | N3 | N2 | N1 | N0 | Fvco   |

|                |    |    |    |    |    |    | (MHz)  |    |    |    |    |    |    |    | (MHz)  |

| 1              | 0  | 0  | 0  | 0  | 0  | 0  | 3.2    | 17 | 0  | 1  | 0  | 0  | 0  | 0  | 7.0    |

| 2              |    |    | 0  | 0  | 0  | 1  | 3.4    | 18 |    |    | 0  | 0  | 0  | 1  | 7.2    |

| 3              |    |    | 0  | 0  | 1  | 0  | 3.6    | 19 |    |    | 0  | 0  | 1  | 0  | 7.5    |

| 4              |    |    | 0  | 0  | 1  | 1  | 3.8    | 20 |    |    | 0  | 0  | 1  | 1  | 7.8    |

| 5              |    |    | 0  | 1  | 0  | 0  | 4.0    | 21 |    |    | 0  | 1  | 0  | 0  | 8.0    |

| 6              |    |    | 0  | 1  | 0  | 1  | 4.2    | 22 |    |    | 0  | 1  | 0  | 1  | Test   |

| 7              |    |    | 0  | 1  | 1  | 0  | 4.5    | 23 |    |    | 0  | 1  | 1  | 0  | Test   |

| 8              |    |    | 0  | 1  | 1  | 1  | 4.8    | 24 |    |    | 0  | 1  | 1  | 1  | Test   |

| 9              |    |    | 1  | 0  | 0  | 0  | 5.0    | 25 |    |    | 1  | 0  | 0  | 0  | Test   |

| 10             |    |    | 1  | 0  | 0  | 1  | 5.2    | 26 |    |    | 1  | 0  | 0  | 1  | Test   |

| 11             |    |    | 1  | 0  | 1  | 0  | 5.5    | 27 |    |    | 1  | 0  | 1  | 0  | Test   |

| 12             |    |    | 1  | 0  | 1  | 1  | 5.8    | 28 |    |    | 1  | 0  | 1  | 1  | Test   |

| 13             |    |    | 1  | 1  | 0  | 0  | 6.0    | 29 |    |    | 1  | 1  | 0  | 0  | Test   |

| 14             |    |    | 1  | 1  | 0  | 1  | 6.2    | 30 |    |    | 1  | 1  | 0  | 1  | Test   |

| 15             |    |    | 1  | 1  | 1  | 0  | 6.5    | 31 |    |    | 1  | 1  | 1  | 0  | Test   |

| 16             |    |    | 1  | 1  | 1  | 1  | 6.8    | 32 |    |    | 1  | 1  | 1  | 1  | Test   |

| 33             | 1  | 0  | 0  | 0  | 0  | 0  | 40.660 | 49 | 1  | 1  | 0  | 0  | 0  | 0  | 49.840 |

| 34             |    |    | 0  | 0  | 0  | 1  | 40.665 | 50 |    |    | 0  | 0  | 0  | 1  | 49.830 |

| 35             |    |    | 0  | 0  | 1  | 0  | 40.670 | 51 |    |    | 0  | 0  | 1  | 0  | 49.860 |

| 36             |    |    | 0  | 0  | 1  | 1  | 40.675 | 52 |    |    | 0  | 0  | _1 | 1  | 49.890 |

| 37             |    |    | 0  | 1  | 0  | 0  | 40.680 | 53 |    |    | 0  | 1  | 0  | 0  | 49.850 |

| 38             |    |    | 0  | 1  | 0  | 1  | 40.685 | 54 |    |    | 0  | 1  | 0  | 1  | 49.880 |

| 39             |    |    | 0  | 1  | 1  | 0  | 40.690 | 55 |    |    | 0  | 1  | 1  | 0  | 49.950 |

| 40             |    |    | 0  | 1  | 1  | 1  | -      | 56 |    |    | 0  | 1  | 1  | 1  | 49.920 |

| 41             |    |    | 1  | 0  | 0  | 0  | 40.700 | 57 |    |    | 1  | 0  | 0  | 0  | 49.900 |

| 42             |    |    | 1  | 0  | 0  | 1  | 40.695 | 58 |    |    | 1  | 0  | 0  | 1  | 49.870 |

| 43             |    |    | 1  | 0  | 1  | 0  | Test   | 59 |    |    | 1  | 0  | 1  | 0  | 49.930 |

| 44             |    |    | 1  | 0  | 1  | 1  | Test   | 60 |    |    | 1  | 0  | 1  | 1  | 49.940 |

| 45             |    |    | 1  | 1  | 0  | 0  | Test   | 61 |    |    | 1  | 1  | 0  | 0  | 49.910 |

| 46             |    |    | 1  | 1  | 0  | 1  | Test   | 62 |    |    | 1  | 1  | 0  | 1  | Test   |

| 47             |    |    | 1  | 1  | 1  | 0  | Test   | 63 |    |    | 1  | 1  | 1  | 0  | Test   |

| 48             |    |    | 1  | 1  | 1  | 1  | Test   | 64 |    |    | 1  | 1  | 1  | 1  | Test   |

### Appendix2: MCD2006R ROM logic table

**Note:** (1) The background letters A~D denote channel group.

- (2) A 20MHz crystal is a must for all groups.

- (3) When pin N0-N5 float, the logic level is low, when the pin is connected to VDD, the logic level is high.

| No | N5 | N4 | N3 | N2 | N1 | N0 | Fvco   | No | N5 | N4 | N3 | N2 | N1 | N0 | Fvco   |

|----|----|----|----|----|----|----|--------|----|----|----|----|----|----|----|--------|

|    |    |    |    |    |    |    | (MHz)  |    |    |    |    |    |    |    | (MHz)  |

| 1  | 0  | 0  | 0  | 0  | 0  | 0  | 45.115 | 17 | 0  | 1  | 0  | 0  | 0  | 0  | 54.285 |

| 2  |    |    | 0  | 0  | 0  | 1  | 45.120 | 18 |    |    | 0  | 0  | 0  | 1  | 54.295 |

| 3  |    |    | 0  | 0  | 1  | 0  | 45.125 | 19 |    |    | 0  | 0  | 1  | 0  | 54.305 |

| 4  |    |    | 0  | 0  | 1  | 1  | 45.130 | 20 |    |    | 0  | 0  | 1  | 1  | 54.375 |

| 5  |    |    | 0  | 1  | 0  | 0  | 45.135 | 21 |    |    | 0  | 1  | 0  | 0  | 54.315 |

| 6  |    |    | 0  | 1  | 0  | 1  | 45.140 | 22 |    |    | 0  | 1  | 0  | 1  | 54.325 |

| 7  |    |    | 0  | 1  | 1  | 0  | 45.145 | 23 |    |    | 0  | 1  | 1  | 0  | 54.405 |

| 8  |    |    | 0  | 1  | 1  | 1  | Test   | 24 |    |    | 0  | 1  | 1  | 1  | 54.345 |

| 9  |    |    | 1  | 0  | 0  | 0  | 45.155 | 25 |    |    | 1  | 0  | 0  | 0  | 54.355 |

| 10 |    |    | 1  | 0  | 0  | 1  | 45.150 | 26 |    |    | 1  | 0  | 0  | 1  | 54.335 |

| 11 |    |    | 1  | 0  | 1  | 0  | Test   | 27 |    |    | 1  | 0  | 1  | 0  | 54.385 |

| 12 |    |    | 1  | 0  | 1  | 1  | Test   | 28 |    |    | 1  | 0  | 1  | 1  | 54.395 |

| 13 |    |    | 1  | 1  | 0  | 0  | Test   | 29 |    |    | 1  | 1  | 0  | 0  | 54.365 |

| 14 |    |    | 1  | 1  | 0  | 1  | Test   | 30 |    |    | 1  | 1  | 0  | 1  | Test   |

| 15 |    |    | 1  | 1  | 1  | 0  | Test   | 31 |    |    | 1  | 1  | 1  | 0  | Test   |

| 16 |    |    | 1  | 1  | 1  | 1  | Test   | 32 |    |    | 1  | 1  | 1  | 1  | Test   |

| 33 | 1  | 0  | 0  | 0  | 0  | 0  | 40.205 | 49 | 1  | 1  | 0  | 0  | 0  | 0  | 49.375 |

| 34 |    |    | 0  | 0  | 0  | 1  | 40.210 | 50 |    |    | 0  | 0  | 0  | 1  | 49.385 |

| 35 |    |    | 0  | 0  | 1  | 0  | 40.215 | 51 |    |    | 0  | 0  | 1  | 0  | 49.395 |

| 36 |    |    | 0  | 0  | 1  | 1  | 40.220 | 52 |    |    | 0  | 0  | 1  | 1  | 49.465 |

| 37 |    |    | 0  | 1  | 0  | 0  | 40.225 | 53 |    |    | 0  | 1  | 0  | 0  | 49.405 |

| 38 |    |    | 0  | 1  | 0  | 1  | 40.230 | 54 |    |    | 0  | 1  | 0  | 1  | 49.415 |

| 39 |    |    | 0  | 1  | 1  | 0  | 40.235 | 55 |    |    | 0  | 1  | 1  | 0  | 49.495 |

| 40 |    |    | 0  | 1  | 1  | 1  | -      | 56 |    |    | 0  | 1  | 1  | 1  | 49.435 |

| 41 |    |    | 1  | 0  | 0  | 0  | 40.245 | 57 |    |    | 1  | 0  | 0  | 0  | 49.445 |

| 42 |    |    | 1  | 0  | 0  | 1  | 40.240 | 58 |    |    | 1  | 0  | 0  | 1  | 49.425 |

| 43 |    |    | 1  | 0  | 1  | 0  | Test   | 59 |    |    | 1  | 0  | 1  | 0  | 49.475 |

| 44 |    |    | 1  | 0  | 1  | 1  | Test   | 60 |    |    | 1  | 0  | 1  | 1  | 49.485 |

| 45 |    |    | 1  | 1  | 0  | 0  | Test   | 61 |    |    | 1  | 1  | 0  | 0  | 49.455 |

| 46 |    |    | 1  | 1  | 0  | 1  | Test   | 62 |    |    | 1  | 1  | 0  | 1  | Test   |

| 47 |    |    | 1  | 1  | 1  | 0  | Test   | 63 |    |    | 1  | 1  | 1  | 0  | Test   |

| 48 |    |    | 1  | 1  | 1  | 1  | Test   | 64 |    |    | 1  | 1  | 1  | 1  | Test   |

### **Important Notice**

MC Devices reserves the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to MC Devices' terms and conditions of sale supplied at the time of order acknowledgment.

MC Devices warrants performance of its products to the specifications applicable at the time of sale in accordance with MC Devices' standard warranty. Testing and other quality control techniques are also support this warranty.

#### 美芯集成电路 (深圳) 有限公司

中国深圳高新区科技中二路软件园一期四栋 516 室

电话: (86) 755-8618-5088 传真: (86) 755-8618-5000 Email: sales@mcdevices.com http://www.mcdevices.com

#### MC DEVICES Co.,Ltd

516 Bld. 4, National Software Park, 2 Kejizhong Rd., Shenzhen Hi-Tech Park, Shenzhen, Guagdong, China

Tel: 86-755-8618-5088

Fax: 86-755-8618-5000

Email: sales@mcdevices.com http://www.mcdevices.com